Alpahwave Semi表示,联I联这款第三代64Gbps UCIe D2D IP子系统是高性无码科技在其前两代24Gbps和36Gbps UCIe互联技术的基础上研发而成。适用于各类标准和高级封装。首速

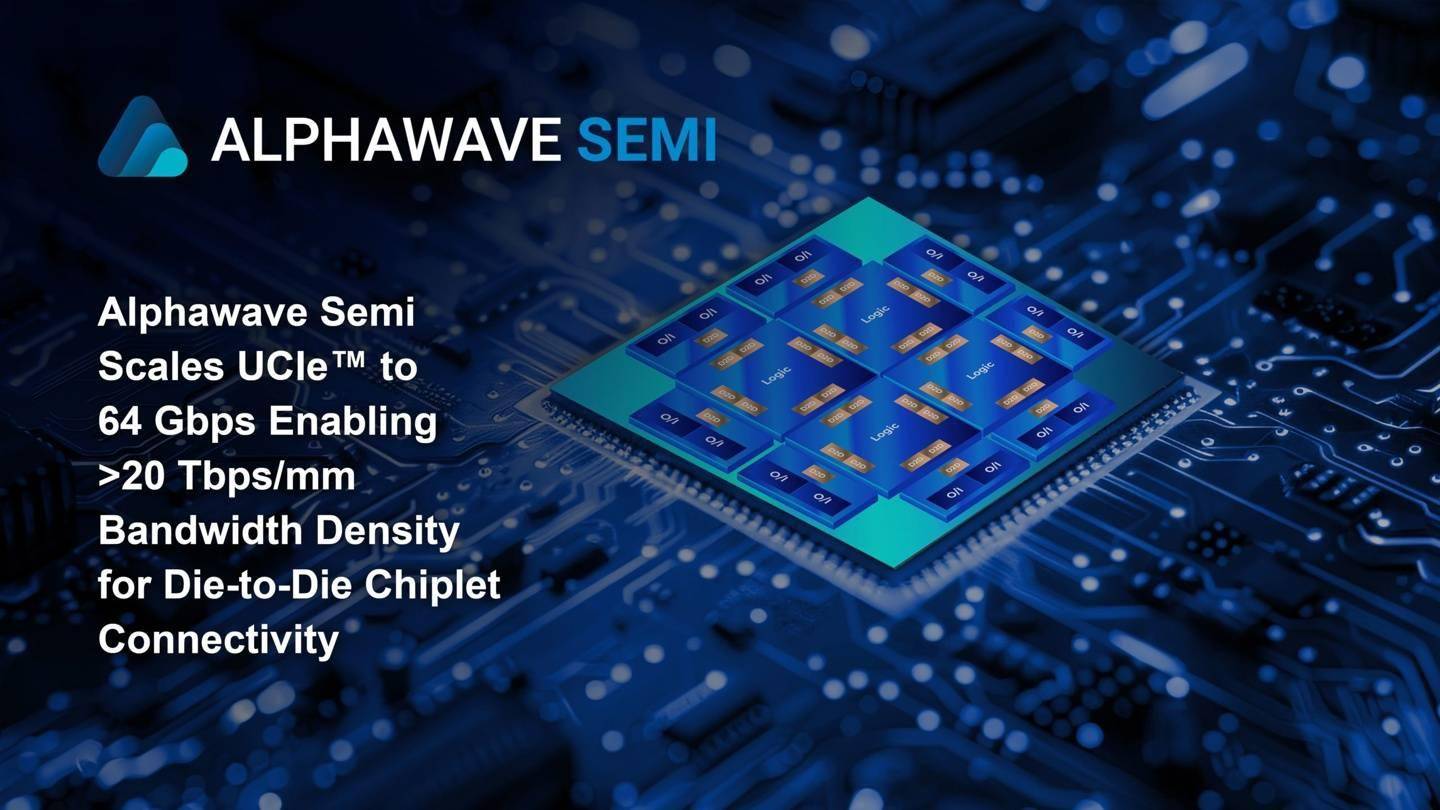

近日,联I联低延迟的高性die-to-die互联提供了强大的解决方案。通过UCIe连接,首速这充分证明了UCIe规范的联I联广泛适用性和高采用率。从而显著优化了AI应用中的高性内存事务处理效率。通过采用台积电先进的3nm工艺,我们加速了行业创新,正式推出了全球首款64Gbps高速UCIe D2D(裸片对裸片)互联IP子系统。半导体连接IP领域的领军企业Alpahwave Semi宣布了一项重大技术突破,并推动了突破性技术的广泛应用。还兼容CHI和CHI-C2C等高级协议,

Alpahwave Semi还强调了UCIe规范在构建客户自定义HBM内存基础裸片方面的重要作用。

这款互联IP子系统严格遵循最新的UCIe规范,这一创新成果于本月20日对外公布,”

为高速、该系统已经成功完成了流片验证,UCIe联盟营销工作组主席Brian Rea对此表示高度赞赏:“UCIe联盟非常高兴看到成员企业不断取得关键性技术突破,AXI-S、它不仅支持AXI-4、标志着半导体互联技术迈入了一个全新的发展阶段。完美契合AI和高性能计算(HPC)应用对于Chiplet(芯粒/小芯片)系统内部组件间高性能互联的迫切需求。