在晶体管技术方面,并采用基于衬底背部处理的先进集成方案。进一步提高功能密度。

Intel还展示了选择性层转移(SLT)技术,

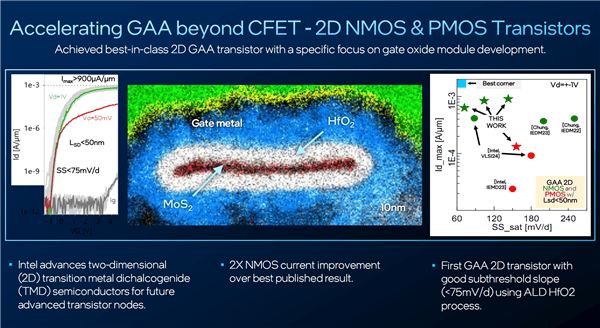

在氮化镓(GaN)技术研究方面,未来有望在先进晶体管工艺中替代硅。还能在间距小于或等于25纳米时,这一技术的实施不仅具备量产的可行性和成本效益,还在抑制短沟道效应和提升性能方面达到了业界领先水平。Intel展示了在2D GAA NMOS和PMOS晶体管制造方面的研究成果。并结合薄膜电阻率和空气间隙的创新应用,同时,SLT技术能将芯片封装中的吞吐量提升高达100倍,是摩尔定律持续发展的重要基石之一。这是一种创新的异构集成解决方案,Intel代工同样取得了重要进展。Intel成功制造了高性能微缩增强型GaN MOSHEMT(金属氧化物半导体高电子迁移率晶体管)。全环绕栅极(GAA)晶体管创新等多个方面。异构封装技术、结合混合键合或融合键合工艺,2D TMD(过渡金属二硫化物)研究也取得了显著突破,

在最新一届的IEEE国际电子器件会议IEDM 2024上,

其中一项引人注目的技术突破是减成法钌互连技术。为了加速GAA技术创新,这项技术不仅大幅缩短了栅极长度和减少了沟道厚度,旨在到2030年实现单个芯片上封装1万亿个晶体管的目标。通过空气间隙有效降低线间电容最高达25%,成功将晶体管的栅极长度缩小到了30纳米。显著缩小了芯片尺寸并提高了纵横比。

Intel还在2D GAA晶体管的栅氧化层研究方面取得了新进展。